English

English  Español

Español Português

Português русский

русский Français

Français 日本語

日本語 Deutsch

Deutsch tiếng Việt

tiếng Việt Italiano

Italiano Nederlands

Nederlands ภาษาไทย

ภาษาไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা ভাষার

বাংলা ভাষার Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türkçe

Türkçe Gaeilge

Gaeilge العربية

العربية Indonesia

Indonesia Norsk

Norsk تمل

تمل český

český ελληνικά

ελληνικά український

український Javanese

Javanese فارسی

فارسی தமிழ்

தமிழ் తెలుగు

తెలుగు नेपाली

नेपाली Burmese

Burmese български

български ລາວ

ລາວ Latine

Latine Қазақша

Қазақша Euskal

Euskal Azərbaycan

Azərbaycan Slovenský jazyk

Slovenský jazyk Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski

How Can a Chip IC Reduce Risk in Your Next Electronics Build?

Abstract

A Chip IC is often the smallest item on a bill of materials, yet it can be the biggest source of delays, field failures, and hidden cost. If you’ve ever dealt with a “works in the lab, fails in the real world” product, surprise component substitutions, or a sudden end-of-life notice, you already know how quickly a project can spiral.

This article breaks down practical ways to choose, validate, and integrate a Chip IC so your product is stable in production—not just in prototyping. You’ll get a clear checklist for selection, reliability guardrails, a simple verification workflow to avoid counterfeits, and a manufacturing-minded approach to PCBA integration. Along the way, I’ll share how teams typically solve these problems with support from Shenzhen Greeting Electronics Co., Ltd., especially when time, yield, and long-term supply are on the line.

Table of Contents

- Outline

- Why Chip IC Decisions Create Big Outcomes

- What “Chip IC” Covers in Real Projects

- Customer Pain Points and What Usually Fixes Them

- A Chip IC Selection Checklist That Prevents Rework

- Integration Into PCBA Without Yield Surprises

- Quality and Reliability Controls That Actually Matter

- Cost and Supply Chain Strategies Without Compromising Safety

- FAQ

- Next Steps

Outline

- Define what “Chip IC” means across functions, packages, and lifecycle risk

- Map common failure modes to specific prevention steps

- Use a selection checklist that covers electrical, mechanical, environmental, and manufacturing constraints

- Integrate the IC with layout, assembly, programming, and test in mind

- Apply practical verification and reliability controls from prototype through mass production

- Balance cost and lead time with a plan for second sources and change control

Why Chip IC Decisions Create Big Outcomes

Teams usually pick a Chip IC based on a fast comparison: “Does it meet the spec and fit the budget?” That’s a good start—but it’s not enough when you’re building something that must survive shipping, temperature swings, ESD events, long duty cycles, and real users doing unpredictable things.

In practice, a “correct” IC on paper can still create problems:

- Schedule risk from long lead times or sudden shortages

- Yield loss from assembly sensitivity, moisture issues, or marginal footprints

- Field failures from thermal stress, ESD, or borderline power integrity

- Requalification pain when parts are substituted without proper control

The goal isn’t perfection—it’s predictability. You want a Chip IC strategy that keeps engineering, manufacturing, and supply chain aligned so your product stays stable from prototype to production.

What “Chip IC” Covers in Real Projects

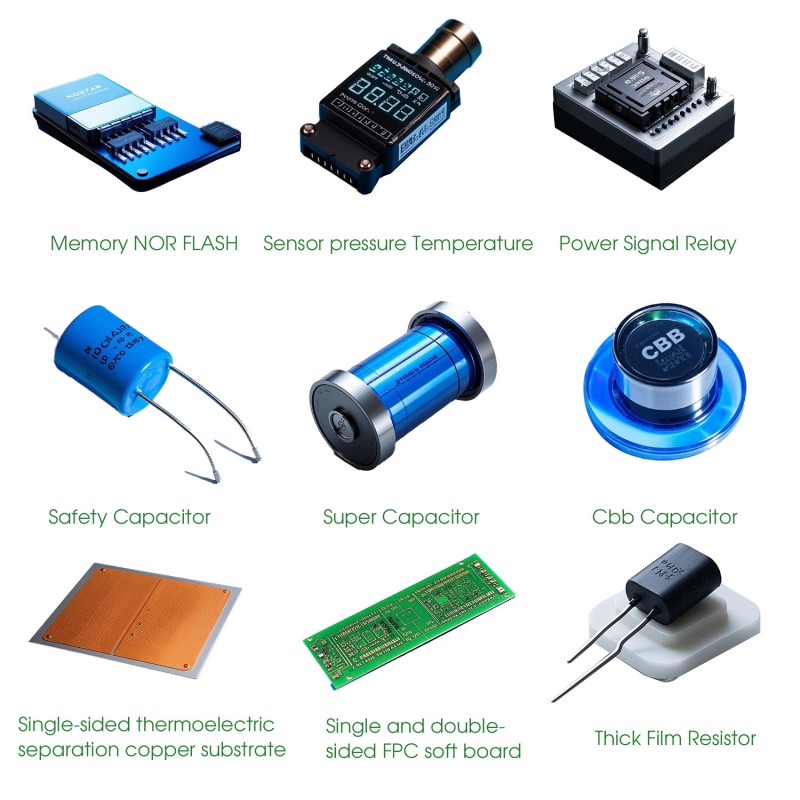

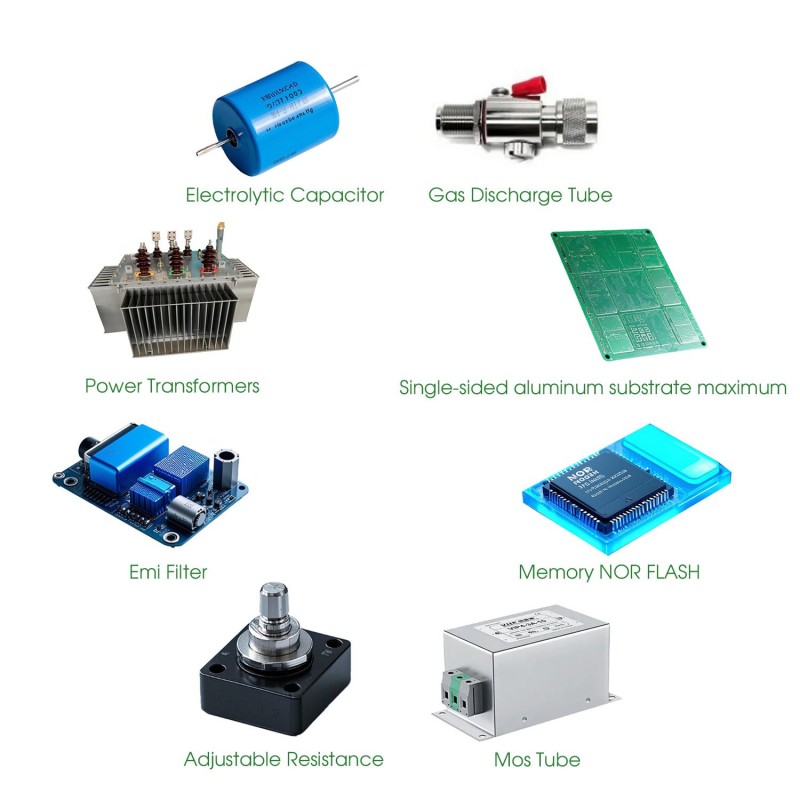

“Chip IC” is a broad, practical umbrella. Depending on your product, it can refer to:

- MCUs and processors (control logic, firmware, connectivity stacks)

- Power ICs (PMICs, DC-DC converters, LDOs, battery management)

- Analog and mixed-signal ICs (ADCs/DACs, op-amps, sensors interfaces)

- Interface and protection ICs (USB, CAN, RS-485, ESD protection arrays)

- Memory and storage (Flash, EEPROM, DRAM)

Two ICs can share similar datasheet numbers and still behave differently in your board because of package type, thermal path, control-loop stability, layout sensitivity, or programming/test needs. That’s why “meets spec” is only one layer of the decision.

Customer Pain Points and What Usually Fixes Them

Here are the issues customers bring up most often when a Chip IC becomes the bottleneck—and the fixes that actually reduce risk.

-

Pain point 1: “We can’t source the exact IC reliably.”

Fix: define an approved alternates list early, lock a change-control process, and validate alternates with a tight electrical + functional test plan. -

Pain point 2: “Our prototype works, but production yield is unstable.”

Fix: review footprint and assembly constraints (stencil, paste, reflow profile, MSL handling), then add boundary tests that catch marginal behavior. -

Pain point 3: “We worry about counterfeit or reclaimed components.”

Fix: implement an incoming verification workflow (traceability, visual inspection, marking checks, sample electrical tests) and use controlled procurement channels. -

Pain point 4: “Power issues show up under load or temperature.”

Fix: treat power integrity and thermal as first-class requirements; validate worst-case corners, not just typical conditions. -

Pain point 5: “We’re losing time on bring-up and debugging.”

Fix: design for test (test points, boundary scan where applicable), and plan programming/firmware loading as part of manufacturing—not an afterthought.

Many teams that want a single partner to coordinate selection support, PCBA integration, sourcing discipline, and production testing work with Shenzhen Greeting Electronics Co., Ltd. because it reduces handoff gaps—where most “surprise failures” tend to hide.

A Chip IC Selection Checklist That Prevents Rework

Use this checklist before you lock the Chip IC into your design. It’s designed to catch the problems that don’t show up in a quick datasheet skim.

- Electrical margins: confirm worst-case voltage, current, temperature, and tolerance stacks—then add margin for real load behavior.

- Package and assembly fit: validate package availability (QFN/BGA/SOIC, etc.), footprint robustness, and whether your assembler can handle the pitch and thermal pad requirements.

- Thermal path: evaluate junction temperature at worst case and confirm you have a realistic heat path (copper pours, vias, airflow assumptions).

- ESD and transient exposure: map real-world exposure (cables, user touch, inductive loads) and decide whether you need external protection ICs or filtering.

- Firmware/programming needs: confirm programming interface, security requirements, and whether production programming will be done inline or offline.

- Testability: define what you will measure in production (power rails, key waveforms, communication handshake, sensor checks) and ensure the board supports it.

- Lifecycle risk: check longevity expectations and create a plan for alternates and last-time buys where necessary.

- Documentation discipline: freeze part numbers, package variants, and revision rules so substitutions don’t become silent failures.

If you do only one thing from this list, do this: write down the “non-negotiables” for the Chip IC (electrical range, package, qualification expectations, programming method) and make every alternate prove it can meet them.

Integration Into PCBA Without Yield Surprises

A Chip IC doesn’t fail in isolation—it fails in a board, inside an enclosure, in a real manufacturing process. Integration is where reliability is either earned or lost.

- Layout matters more than you want it to: sensitive ICs (high-speed, switching power, RF) can be “correct” yet unstable if routing, grounding, or decoupling is sloppy.

- Decoupling is not decorative: place capacitors as intended, minimize loop area, and validate ripple and transient response under worst-case loads.

- Reflow and MSL handling: moisture-sensitive packages can crack or delaminate if storage and bake rules aren’t followed.

- Stencil and paste printing: fine-pitch packages and thermal pads need paste control to prevent tombstoning, bridging, or voiding.

- Programming flow: plan fixture access and define how you’ll verify firmware version and configuration at the end of line.

A good habit is to treat your first pilot run like a learning experiment. Track defect types, locations, and conditions, then close the loop with layout tweaks or process updates before scaling volume.

Quality and Reliability Controls That Actually Matter

Reliability is not a vibe. It’s a set of checks that catch the failure modes you’re most likely to see in the field. The table below is a practical menu—pick what matches your product’s risk profile.

| Control | What It Catches | Practical Implementation |

|---|---|---|

| Incoming verification (sampling) | Counterfeit, wrong variant, remarking | Traceability checks + visual inspection + basic electrical ID tests |

| Power rail margin test | Brownouts, unstable regulators, load transients | Test at min/max input, max load, temperature corners |

| Thermal soak / burn-in (as needed) | Early-life failures, marginal solder joints | Run functional test under heat for a defined duration |

| ESD/transient validation | User-touch failures, cable events, inductive kickback | Apply realistic events to I/O and verify no latch-up or resets |

| Firmware/configuration verification | Wrong firmware, wrong region config, calibration misses | End-of-line readback + version logging + pass/fail rules |

If your product ships into harsh environments, prioritize thermal and transient validation. If your product ships at high volume, prioritize testability and incoming verification so defects don’t multiply across batches.

Cost and Supply Chain Strategies Without Compromising Safety

Cost control is real—and necessary. But cost cutting around a Chip IC can quietly introduce risk if it removes traceability, weakens incoming checks, or encourages uncontrolled substitutions.

- Define “allowed substitutions” in writing: same electrical grade, same package, same qualification expectations. Anything else triggers revalidation.

- Use a two-layer sourcing plan: primary channel for stability; secondary for contingency—both vetted and traceable.

- Keep alternates warm: don’t wait until a shortage happens. Build a small batch with alternates and run your acceptance tests now.

- Track lot and date codes: it helps you isolate issues fast if a defect cluster appears.

- Plan for lifecycle events: if an IC is likely to go end-of-life within your product’s support window, design in a migration path early.

A practical way to stay sane is to connect engineering rules (what’s acceptable) with purchasing rules (what’s allowed to be bought) so the system doesn’t drift under deadline pressure.

FAQ

Q: What should I validate first when choosing a Chip IC?

A: Start with worst-case electrical margins and package/manufacturing fit. If the IC can’t be assembled reliably or it runs hot at your worst load, everything else becomes damage control.

Q: How do I reduce the risk of counterfeit Chip ICs?

A: Require traceability, avoid uncontrolled spot buys, and add incoming sampling checks (marking, packaging, and quick electrical verification). For higher-risk builds, increase sample size and log results by lot.

Q: Why does my power IC behave differently on the final board than on the eval board?

A: Layout, grounding, and component placement often change the control-loop behavior and noise environment. Validate with your exact PCB, your exact load profile, and your real wiring/cables.

Q: Do I need burn-in for every product?

A: Not always. Burn-in is most useful when early-life failures would be costly, when field access is hard, or when you see marginal defects in pilot runs. Otherwise, strong functional testing and incoming verification may be more efficient.

Q: How can I avoid delays caused by IC lead times?

A: Lock alternates early, validate them before you’re forced to switch, and keep your purchasing rules aligned with engineering’s approved list so substitutions don’t happen quietly.

Q: What makes a Chip IC “production-ready”?

A: It’s not only about passing a prototype demo. Production-ready means the IC is sourceable with traceability, assembles with stable yield, passes consistent end-of-line tests, and holds up under your environmental and transient conditions.

Next Steps

If you want your Chip IC decisions to stop being a gamble, treat selection, sourcing, assembly, and testing as one connected system. That’s how you prevent the classic loop of “prototype success → pilot surprises → production delays.”

At Shenzhen Greeting Electronics Co., Ltd., we help teams turn Chip IC uncertainty into a controlled plan—from selection support and PCBA integration to verification workflows and production testing. If you’re facing shortages, yield instability, or reliability concerns, tell us your application, target environment, and volume, and we’ll suggest a practical path forward.

Ready to move faster with less risk? Share your BOM and requirements and contact us to discuss a reliable Chip IC and PCBA strategy tailored to your product.